Af Jørgen Sarlvit Larsen, illustrationer: CEA Leti

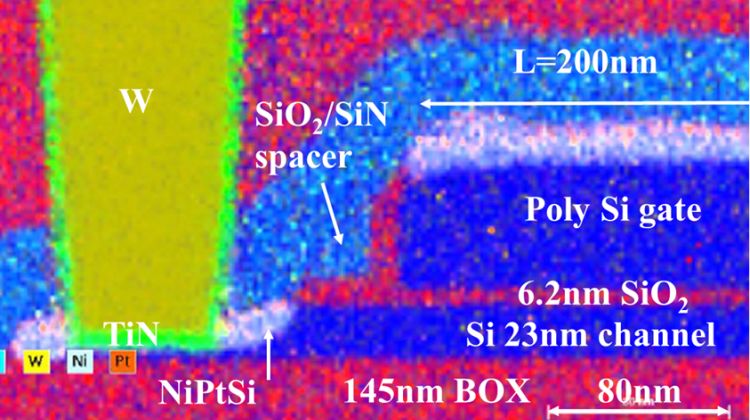

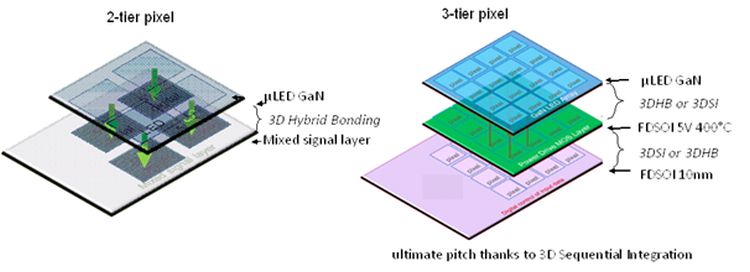

På IEDM 2025 konferencen i San Francisco primo december kunne CEA-Leti rapportere om en væsentlig milepæl for næste generation af 3D chip-stacking, nemlig fuldt funktionsdygtige 2,5 V SOI CMOS-komponenter fremstillet ved 400ºC. Komponenterne matcher den elektriske performance af komponenter fabrikeret ved den hidtidige standardtemperatur (>1000 ºC), hvilket fjerner een af de sidste barrierer for sekventiel 3D integration, der er et hovedmål for det europæiske pilotlinie projekt, FAMES Pilot Line, som koordineres af CEA-Leti. Gennembruddet er muliggjort takket være dette franske forskningsinstituts ekspertise i lavtemperaturprocesser (nanosekund laser hærdning og solid state epitaksial gen-groning), og forskningen tilbyder sand 3 dimensional chipstabling fra lab til fab. Samtidig er tætheden af interkonnektion forbindelserne mellem lagene i den sekventielle 3D integration den højeste blandt 3D teknologierne, såsom TSV og hybrid bonding. CEA-Leti påviste, at SI CMOS er BEOL (back-end og line) kompatibel og således kan stables sikkert over BEOL, mens transistorerne stort set klarer de andre teknologiske optioner fra state-of-the-art løsningerne ved den lave procestemperatur. Det præsenterede indlæg på IEDM 2025 har titlen, “High Performance 2.5 V n&p 400 °C SOI MOSFETs: A Breakthrough for Versatile 3D Sequential Integration”.

– Det er en betydelig milepæl for FAMES projektet, da det muliggør innovative, nye chip-arkitekturer. Og vor lavtemperatur proces kan accelerere virkelige demonstrationer af flerlags stakke ved at kombinere avanceret CMOS logik med smart pixel eller RF lag for at frembringe nye højtydende 3D chips, sagde Dominique Noquet, CEA-Leti vicepræsident og koordinator af FAMES projektet.

– Den 400ºC proces muliggør sekventiel 3D-stacking på ethvert substrat, og det er et stort skridt fremad, fordi det er langt mere udviklet i form af pålidelighed og skalerbarhed end nuværende lavtemperaturs løsninger, såsom polykrystallinske film, oxid halvledere eller carbon nanotubes, tilføjede Noquet.

– Vores styrke er at kunne håndtere den kolde proces, især nanosekund laser hærdningen, for at opnå CMOS enheder med høj mobilitet og høj pålidelighed ved lav temperatur. Specielt er laser ekspertisen med til at gøre vor metode unik, fremhævede Daphnée Bosch, ledende forfatter af indlægget.