Højhastighedskredsløbsteknologier og siliciummålingsresultater af MCU-testchip præsenteret under ISSCC 2024.

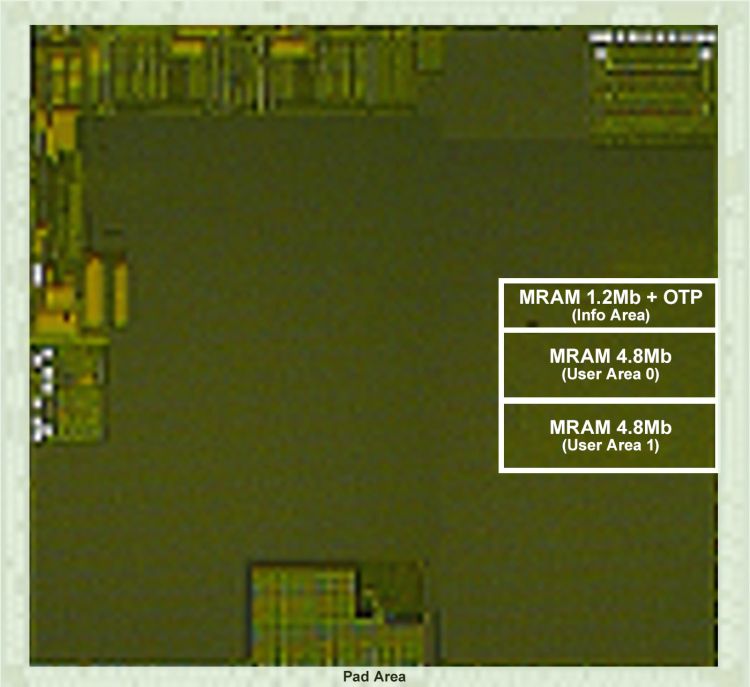

Renesas Electronics Corporation annoncerer, at det har udviklet kredsløbsteknologier i en embedded spin-overførsels momentmagnetoresistiv random-access memory (STT-MRAM eller bare MRAM) testchip med hurtige læse- og skriveoperationer fremstillet ved hjælp af en 22-nm-proces. MCU-testchippen inkluderer en 10,8 megabit (Mbit) indlejret MRAM-hukommelsescellearray. Den opnår en random readaccess-frekvens på over 200 MHz og et write-throughput på 10,4 megabyte pr. sekund (MB/s).

Renesas præsenterede disse resultater den 20. februar på International Solid-State Circuits Conference 2024 (ISSCC 2024), afholdt mellem den 18. og 22. februar 2024 i San Francisco.

I takt med at IoT- og AI-teknologier fortsætter med at udvikle sig, forventes MCU’er, der bruges i endpoints at levere højere ydeevne end nogensinde. CPU-klokfrekvenserne for højtydende MCU’er er i hundredvis af MHz, så for at opnå større ydeevne skal læsehastighederne for indlejret ikke-flygtig hukommelse øges for at minimere afstanden mellem dem og CPU-clockfrekvenserne. MRAM har en mindre read-margin end de flashhukommelser, der bruges i konventionelle MCU’er, hvilket gør højhastighedslæsning vanskeligere. På den anden side, for write-ydelsen, er MRAM hurtigere end flash-hukommelse, fordi det ikke kræver nogen erase, før man udfører write-handlinger. Forkortelse af write-tider er dog ønskelig ikke kun til daglig brug, men også for at reducere omkostningerne ved at skrive testmønstre i testprocesser og skrive kontrolkoder hos slutproduktproducenter.

For at løse disse udfordringer har Renesas udviklet følgende nye kredsløbsteknologier for at opnå hurtigere læse- og skriveoperationer i MRAM.

Fast Read Technology

MRAM-aflæsning udføres generelt af en differentialforstærker for at bestemme, hvilken af hukommelsescellestrømmen eller referencestrømmen, der er størst. Men fordi forskellen i hukommelsescellestrømme mellem 0- og 1-tilstandene (read-vinduet) er mindre for MRAM end for flashhukommelse, skal referencestrømmen placeres præcist i midten af read-vinduet for hurtigere aflæsning. Den nyudviklede teknologi introducerer to mekanismer. Den første mekanisme justerer referencestrømmen i midten af vinduet i overensstemmelse med den aktuelle strømfordeling af hukommelsescellerne for hver chip målt under testprocessen. Den anden mekanisme reducerer forskydningen af sense-forstærkeren. Med disse justeringer opnås hurtigere læsehastighed.

Desuden er der i konventionelle konfigurationer stor parasitisk kapacitans i de kredsløb, der bruges til at styre spændingen af bitlinjen, så den ikke stiger for højt under læseoperationer. Dette forsinker læseprocessen, så en kaskadeforbindelse anvendes i dette kredsløb for at reducere parasitisk kapacitans og fremskynde read-funktioenr.

Takket være disse fremskridt kan Renesas opnå verdens hurtigste tilfældige readaccess-tid på 4,2ns. Selv under hensyntagen til setup-tiden for interfacekredsløbet, der behandler MRAM-udgangsdataene, kan man realisere en random read-operation ved frekvenser på over 200 MHz.

Fast Write Technology

Allerede i 2021 opnåede Renesas et forbedret write-throughput ved først at påføre write-spænding samtidigt til alle bits i en write-enhed ved hjælp af en relativt lav write-spænding genereret fra den eksterne spænding (IO-effekt) af MCU-chippen gennem et step-down-kredsløb og brugte derefter kun en højere write-spænding for de resterende få bits, der ikke kunne overskrives. Denne gang tager Renesas højde for, at fordi strømforsyningsforholdene, der bruges i testprocesser og af slutproduktproducenter, er stabile, kan den nedre spændingsgrænse for den eksterne spænding lempes. Ved at indstille den højere nedtrapningsspænding fra den eksterne spænding, der skal anvendes på alle bits i den første fase, kan skrivegennemstrømningen således forbedres 1,8 gange.

Ved at kombinere ovenstående nye teknologier blev en prototype MCU-testchip med et 10,8 Mbit MRAM-hukommelsescellearray fremstillet ved hjælp af en 22 nm indlejret MRAM-proces. Evaluering af prototypechippen bekræftede, at den opnåede en tilfældig læseadgangsfrekvens på over 200 MHz og en skrivegennemstrømning på 10,4 MB/s ved en maksimal overgangstemperatur på 125°C.

Testchippen indeholder også 0,3 Mbit OTP, der bruger MRAM-hukommelsescelleopdeling til at forhindre forfalskning af data. Denne hukommelse kan bruges til at gemme sikkerhedsoplysninger. At skrive til OTP kræver en højere spænding end skrivning til MRAM, hvilket gør det sværere at udføre skrivning i marken, hvor strømforsyningsspændingerne ofte er mindre stabile. Men ved at undertrykke parasitisk modstand i hukommelsescellearrayet gør denne nye teknologi også skrivning i marken muligt.

Renesas fortsætter med at udvikle teknologier til indlejring af MRAM i MCU’er. Disse nye teknologier har potentialet til dramatisk at øge hukommelsesadgangshastigheden til over 200 MHz, hvilket muliggør højere ydeevne MCU’er med indlejret MRAM. Hurtigere skrivehastighed vil bidrage til mere effektiv kodeskrivning til slutpunktsenheder. Renesas er forpligtet til yderligere at øge kapaciteten, hastigheden og strømeffektiviteten af MRAM.